RISC and CISC Architecture

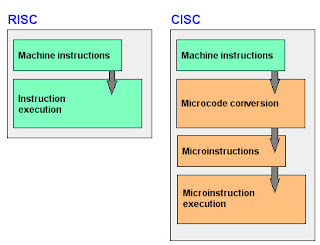

The architecture of the Central Processing Unit (CPU) operates the capacity to function from “Instruction Set Architecture” to where it was designed. The architectural design of the CPU is Reduced instruction set computing (RISC) and Complex instruction set computing (CISC). CISC has the capacity to perform multi-step operations or addressing modes within one instruction set. It is the CPU design where one instruction works several low-level acts. For instance, memory storage, loading from memory, and an arithmetic operation. Reduced instruction set computing is a Central Processing Unit design strategy based on the vision that basic instruction set gives a great performance when combined with a microprocessor architecture which has the capacity to perform the instructions by using some microprocessor cycles per instruction. This article discusses the difference between the RISC and CISC architecture. The hardware part of the Intel is named as Complex Instruction Set Computer (CISC), and Apple hardware is Reduced Instruction Set Computer (RISC).

What is RISC?(designed to reduce the execution time of computer by simplifying the instruction set of a computer where each instruction in one cycle will be performed use in apple ipad,smart mobile etc.)

A reduced instruction set computer is a computer which only uses simple commands that can be divided into several instructions which achieve low-level operation within a single CLK cycle, as its name proposes “Reduced Instruction Set”.

RISC Architecture

The term RISC stands for ‘’Reduced Instruction Set Computer’’. It is a CPU design plan based on simple orders and acts fast.

This is small or reduced set of instructions. Here, every instruction is expected to attain very small jobs. In this machine, the instruction sets are modest and simple, which help in comprising more complex commands. Each instruction is of the similar length; these are wound together to get compound tasks done in a single operation. Most commands are completed in one machine cycle. This pipelining is a crucial technique used to speed up RISC machines.

What is CISC?

A complex instruction set computer is a computer where single instructions can perform numerous low-level operations like a load from memory, an arithmetic operation, and a memory store or are accomplished by multi-step processes or addressing modes in single instructions, as its name proposes “Complex Instruction Set ”.

CISC Architecture

The term CISC stands for ‘’Complex Instruction Set Computer’’. It is a CPU design plan based on single commands, which are skilled in executing multi-step operations.

CISC computers have small programs. It has a huge number of compound instructions, which takes a long time to perform. Here, a single set of instruction is protected in several steps; each instruction set has additional than 300 separate instructions. Maximum instructions are finished in two to ten machine cycles. In CISC, instruction pipelining is not easily implemented.

difference between RISC and CISC Architecture:| 1. RISC stands for Reduced Instruction Set Computer. | 1. CISC stands for Complex Instruction Set Computer. |

| 2. RISC processors have simple instructions taking about one clock cycle. The average clock cycle per instruction (CPI) is 1.5(CPI mean the average number of clock cycles per instruction for a program) | 2. CSIC processor has complex instructions that take up multiple clocks for execution. The average clock cycle per instruction (CPI) is in the range of 2 and 15. |

| 3. Performance is optimized with more focus on software | 3. Performance is optimized with more focus on hardware. |

| 4. It has no memory unit and uses a separate hardware to implement instructions.. | 4. It has a memory unit to implement complex instructions. |

| 5. It has a hard-wired unit of programming. | 5. It has a microprogramming unit. |

| 6. The instruction set is reduced i.e. it has only a few instructions in the instruction set. Many of these instructions are very primitive.(Primitive types are basic programming language building blocks.) | 6. The instruction set has a variety of different instructions that can be used for complex operations. |

| 7. The instruction set has a variety of different instructions that can be used for complex operations. | 7. CISC has many different addressing modes and can thus be used to represent higher-level programming language statements more efficiently. |

| 8. Complex addressing modes are synthesized using the software. | 8. CISC already supports complex addressing modes |

| 9. Multiple register sets are present | 9. Only has a single register set |

| 10. RISC processors are highly pipelined | 10. They are normally not pipelined or less pipelined |

| 11. The complexity of RISC lies with the compiler that executes the program | 11. The complexity lies in the microprogram |

| 12. Execution time is very less | 12. Execution time is very high |

| 13. Code expansion can be a problem | 13. Code expansion is not a problem |

| 14. Decoding of instructions is simple. | 14. Decoding of instructions is complex |

| 15. It does not require external memory for calculations | 15. It requires external memory for calculations |

| 16. The most common RISC microprocessors are Alpha, ARC, ARM, AVR, MIPS, PA-RISC, PIC, Power Architecture, and SPARC. | 16. Examples of CISC processors are the System/360, VAX, PDP-11, Motorola 68000 family, AMD and Intel x86 CPUs. |

| 17. RISC architecture is used in high-end applications such as video processing, telecommunications and image processing. | 17. CISC architecture is used in low-end applications such as security systems, home automation, etc. |

Comments

Post a Comment